Table of Contents

Designing a 32-bit Arithmetic and Logic Unit (ALU) in VHDL involves defining an entity that can perform various arithmetic and logic operations such as addition, subtraction, multiplication, division, and bitwise operations (AND, OR, XOR). Here’s a structured approach to creating this ALU:

1. Define the Entity

The entity will have two 32-bit input operands, a control signal to select the operation, and a 32-bit output.

2. Define the Architecture

In the architecture, we will implement the logic for each operation and use the control signal to select the appropriate result.

3. Write the VHDL Code

Here is a basic implementation of a 32-bit ALU in VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.ALL;

entity ALU is

Port (

A : in STD_LOGIC_VECTOR(31 downto 0);

B : in STD_LOGIC_VECTOR(31 downto 0);

ALU_Sel : in STD_LOGIC_VECTOR(2 downto 0);

Result : out STD_LOGIC_VECTOR(63 downto 0)

);

end ALU;

architecture Behavioral of ALU is

begin

process(A, B, ALU_Sel)

begin

case ALU_Sel is

when "000" => -- Addition

Result <= std_logic_vector(resize(unsigned(A), 64) + resize(unsigned(B), 64));

when "001" => -- Subtraction

Result <= std_logic_vector(resize(unsigned(A), 64) - resize(unsigned(B), 64));

when "010" => -- Multiplication

Result <= std_logic_vector(unsigned(A) * unsigned(B));

--Result <= std_logic_vector(Mul_Result);

when "011" => -- Division

if B /= "00000000000000000000000000000000" then

Result <= std_logic_vector(resize(unsigned(A) / unsigned(B), 64));

else

Result <= (others => '0'); -- Division by zero results in zero

end if;

when "100" => -- AND

Result <= "00000000000000000000000000000000" & (A and B);

when "101" => -- OR

Result <= "00000000000000000000000000000000" & (A or B);

when "110" => -- XOR

Result <= "00000000000000000000000000000000" & (A xor B);

when others =>

Result <= (others => '0'); -- Default case

end case;

end process;

end Behavioral;

4. Explanation:

- Entity Declaration: The entity

ALUhas three inputs: two 32-bit vectors (AandB) and a 3-bit control signal (ALU_Sel). The output is a 64-bit vector (Result). - Architecture: The architecture contains a process that is sensitive to changes in

A,B, andALU_Sel. - Inside the process, a

casestatement is used to select the operation based on the value ofALU_Sel:"000": Addition"001": Subtraction"010": Multiplication"011": Division (with a check to avoid division by zero)"100": Bitwise AND"101": Bitwise OR"110": Bitwise XORothers: Default case to handle unexpected values ofALU_Sel

5. Testing the ALU

To test the ALU, you can create a testbench in VHDL that applies different values to A, B, and ALU_Sel, and checks the output Result for correctness.

6. Testbench Example

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity ALU_tb is

end ALU_tb;

architecture Behavioral of ALU_tb is

-- Component Declaration for the ALU

component ALU

Port (

A : in STD_LOGIC_VECTOR(31 downto 0);

B : in STD_LOGIC_VECTOR(31 downto 0);

ALU_Sel : in STD_LOGIC_VECTOR(2 downto 0);

Result : out STD_LOGIC_VECTOR(31 downto 0)

);

end component;

-- Inputs

signal A : STD_LOGIC_VECTOR(31 downto 0) := (others => '0');

signal B : STD_LOGIC_VECTOR(31 downto 0) := (others => '0');

signal ALU_Sel : STD_LOGIC_VECTOR(2 downto 0) := (others => '0');

-- Outputs

signal Result : STD_LOGIC_VECTOR(31 downto 0);

begin

-- Instantiate the ALU

uut: ALU Port map (

A => A,

B => B,

ALU_Sel => ALU_Sel,

Result => Result

);

-- Stimulus process

stim_proc: process

begin

-- Test Addition

A <= "00000000000000000000000000000101"; -- 5

B <= "00000000000000000000000000000111"; -- 7

ALU_Sel <= "000";

wait for 10 ns;

-- Test Subtraction

ALU_Sel <= "001";

wait for 10 ns;

-- Test Multiplication

ALU_Sel <= "010";

wait for 10 ns;

-- Test Division

ALU_Sel <= "011";

wait for 10 ns;

-- Test AND

ALU_Sel <= "100";

wait for 10 ns;

-- Test OR

ALU_Sel <= "101";

wait for 10 ns;

-- Test XOR

ALU_Sel <= "110";

wait for 10 ns;

-- End simulation

wait;

end process;

end Behavioral;

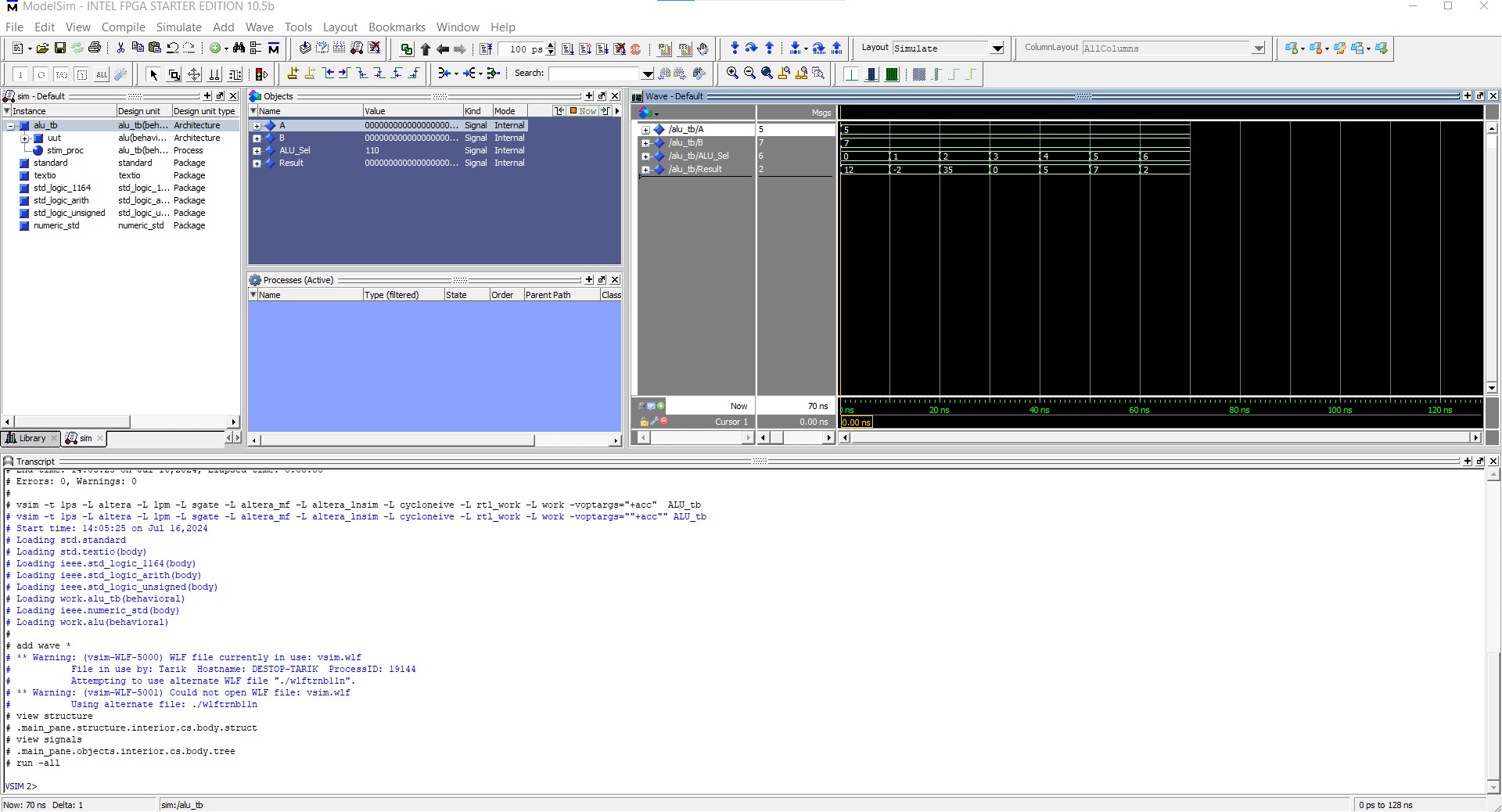

- ModelSim Simulation

7. Explanation:

- Testbench Entity: The testbench does not have any ports.

- Architecture: The architecture of the testbench instantiates the ALU and provides stimulus to it.

- The

stim_procprocess applies different values toA,B, andALU_Sel, and waits for a short time between each operation to observe the results.

This VHDL code provides a solid foundation for a 32-bit ALU that performs the specified operations. You can expand and refine it further based on your project's requirements and testing needs.

🏷️ Author position : Embedded Software Engineer

🔗 Author LinkedIn : LinkedIn profile

Comments